Hello RISC-V !

In the following posts, I will document the environment preparation for working with the RISC-V architecture from the RISC-V association. RISC-V is an open ISA, applying that any vendor can implement.

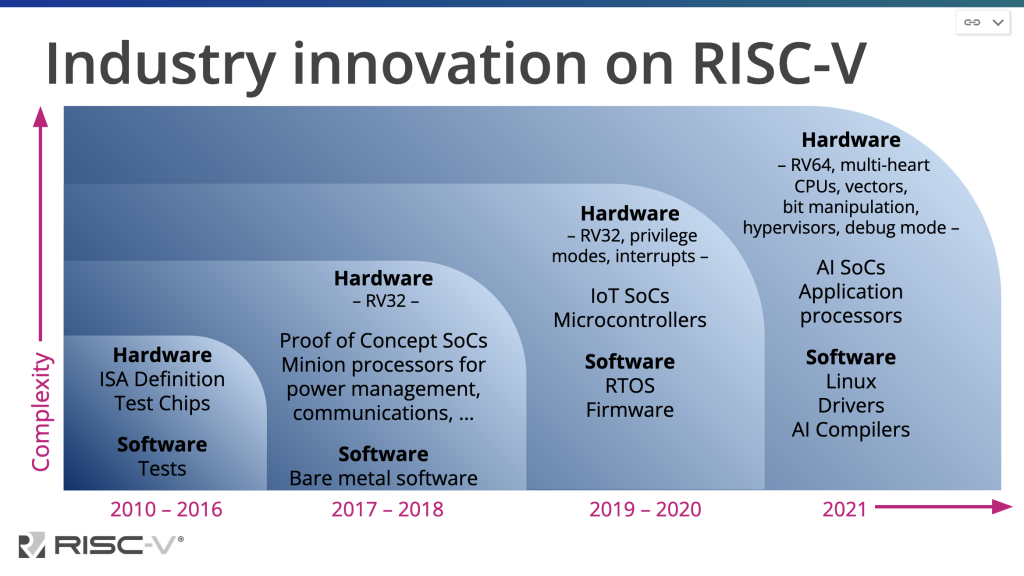

As the industry is waking up around this architecture, I thought it was a good opportunity to get familiar with it; hopefully, the OpenSource principles will help this architecture thrive.

First things first, we need a compiler and toolchain, and for the lack of hardware a simulator. Installing the RISC-V toolchain in brew will help us with that, for OSX we can use the brew tap for the RISC-V to make things easier:

$ brew tap riscv-software-src/riscv

$ brew install riscv-toolsYou could also build your own toolchain manually, but that’s tedious; it’s been a long time without doing that 🙂 .. http://osblog.stephenmarz.com/ch0.old.html